Entwicklung, Analyse und Validierung von Regelalgorithmen auf der Zielhardware

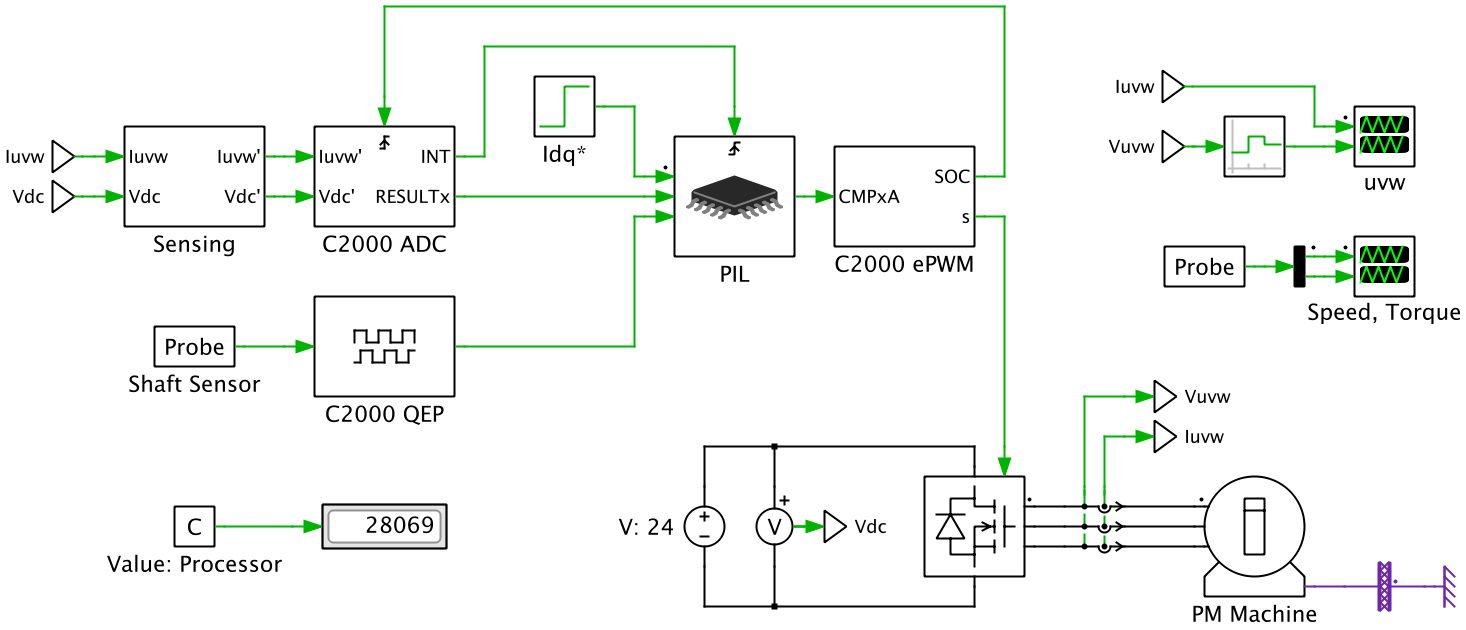

Bei der Entwicklung von digitalen Regelalgorithmen testen die Entwickler ihren Code meist, indem sie ihn innerhalb eines Schaltungssimulators ausführen.

Mit dem PLECS PIL-Paket kann dagegen der Code direkt auf dem realen Prozessor ausgeführt werden, der in die virtuelle Umgebung eines PLECS-Modells eingebunden wird.

Anstatt die Messsignale der Sensoren auszulesen, verwendet der Prozessor die von der Simulation berechneten Werte. Die vom Prozessor mit den Regelalgorithmen berechneten Steuersignale werden zurück in die Simulation geführt und steuern dort die virtuelle Umgebung.

Auf diese Weise können plattformspezifische Software-Defekte wie Überlauf- und Typumwandlungsfehler entdeckt werden. Mit PIL können auch Probleme wie Jitter und Schreib-Lese-Konflikte aufgedeckt und analysiert werden, die bei der parallelen Ausführung von Regelalgorithmen entstehen können.

Komponenten

Der in der Bibliothek enthaltene PIL-Block dient als Schnittstelle zwischen dem Simulationsmodell und dem Prozessor. Zusätzlich enthält die Bibliothek eine Sammlung detaillierter Verhaltensmodelle zur Modellierung der Prozessor-Peripherie wie ADC, PWM oder Capture.

Embedded Framework

Das PLECS PIL-Paket enthält PIL-Framework Bibliotheken für Prozessorfamilien, die in der Leistungselektronik verwendet werden. Um den Prozessor effizient mit dem Simulationsprogramm zu verbinden, unterstützt das Framework verschiedene Kommunikations-Schnittstellen des Prozessors.

Unterstütze Prozessoren

Derzeit werden die folgenden Mikroprozessoren unterstützt:

- TI C2000 Familie (einschließlich Delfino Dual-Core Prozessoren)

- ST STM32F4 Serie

- Microchip dsPIC33F (MC Version)