# Embedded Code Generation DEMO MODEL

# Simple SPI Model

A simple model to explore the SPI protocol with the TI C2000 TSP

Last updated in C2000 TSP 1.5.2

- ▶ Request a PLECS and PLECS Coder trial license

- ► Get the latest TI C2000 and RT Box Target Support Package

- ► Check the PLECS, RT Box and TI C2000 TSP documentation

# 1 Overview

This demo features a simple model using the Serial Peripheral Interface (SPI) blocks on Texas Instruments (TI) C2000 microcontrollers (MCUs) with the PLECS Coder and the TI C2000 Target Support Package.

The SPI is a high-speed synchronous serial input/output device that allows a serial bit stream of programmable length (1 to 16 bits) to be shifted into and out of the device at a configurable bit-transfer rate. The SPI is usually used for communications between the MCU controller and external peripherals, or another controller.

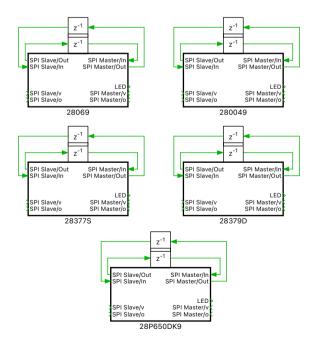

The model is split into five distinct subsystems called "28069", "280049", "28377S", "28379D", and "28P650DK9". Each subsystem can be independently deployed to the corresponding TI C2000 Launch-Pad hardware. The following sections provide a brief description of the model and instructions on how to simulate it.

# 2 Model

The top level schematic contains four separate subsystems, as shown in Fig. 1. The subsystem labeled "28069" is configured for the TI 28069 LaunchPad [2], the subsystem labeled "280049" is configured for the TI 280049C LaunchPad [1], the subsystem labeled "28377S" is configured the TI 28377S LaunchPad [3], the subsystem labeled "28379D" is configured for the TI 28379D LaunchPad [4], and lasly the subsystem labeled "28P650DK9" is configured for the TI 28P650DK9 LaunchPad[5].

Each subsystem is enabled for code generation, as indicated by the thick outer border of the subsystem blocks. This step is necessary to generate the model code for a subsystem via the PLECS Coder. This setting is configured by selecting the subsystem, opening **Edit + Subsystem + Execution settings...** menu, and then selecting the **Enable code generation** option.

Figure 1: Top level schematic of the model with four subsystems

The SPI is a master-slave based interface with a single master and one or more slave devices.

The interface consists of the following signals:

- SPISIMO Serial data output (master out/slave in)

- SPISOMI Serial data input (master in/slave out)

- SPICLK Shift-clock, generated by the SPI Master

- /SPICS Chip-select or slave-enable signal, also referred to as SPISTE. The chip-select signal is an active-low signal that enables the SOMI and SIMO ports of the SPI Slave

The SPI Master block provides a clock signal (SPICLK) which generates a configurable number of clock pulses during each simulation step. For both the slave and the master, data is shifted out of the shift registers on one edge (rising or falling) of the SPICLK and latched into the shift register on the opposite clock edge. If the clock phase (CPHA) bit is configured to 1, data is transmitted and received a half-cycle before the SPICLK transition.

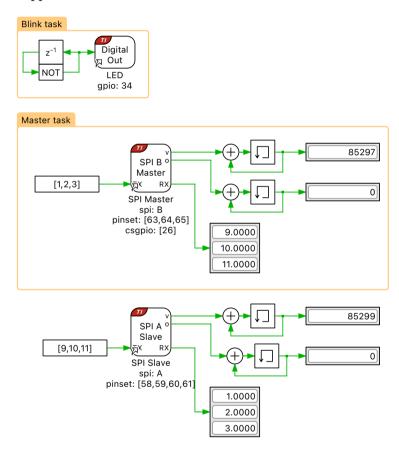

In this model, each of the subsystems includes a simple SPI model, illustrating signal exchange between one SPI Master and one SPI Slave of the same MCU target, as shown in Fig. 2. To explore the signal exchange via SPI between two different MCU targets, choose any two desired targets. Then configure one of them as a SPI Master and the other one as a SPI Slave.

Multiple SPI Slaves can be supported by a single master through chip-select (/CS) signals. For details on multiple SPI Slaves, refer to the "Help" section of the SPI Master block, or refer to the TI C2000 Target Support User Manual [6].

Figure 2: Schematic of the subsystem labeled 28379D

For both SPI Master and SPI Slave blocks, the data to be transmitted is provided at the input **TX** and the data received is available at the output **RX**.

#### **Considerations for SPI Master**

An output value of 1 at the  $\mathbf{v}$  port of the SPI Master indicates that valid data is sent to all the slaves. If the SPI Master does not have enough time to complete the transmission before the block is executed again, the output  $\mathbf{o}$  turns 1 to indicate an overrun error. In the model, as shown in Fig. 2, a counter logic is included at the  $\mathbf{v}$  and  $\mathbf{o}$  ports. This doesn't have much meaning offline.

If an overrun error is being signaled at the o port of the SPI Master, it is possible that the task with which the SPI Master is associated executes too fast. In this case, either reduce the SPI Master execution task rate or increase the SPI clock rate.

For example, if SPICLK is set as 180000 Hz, and is expected to transmit a packet of 4 words at 8 bits per word, then the time it would take to transmit one packet is

$$\frac{1}{180000}*4*8 = 1.78*10^{-4} \text{ seconds}$$

In this case, the execution step size of the SPI Master must be set to values greater than 0.178 milliseconds.

#### **Considerations for SPI Slave**

An output value of 1 at the  $\mathbf{v}$  port indicates a valid data exchange with the SPI Master. If the SPI  $\mathbf{RX}$  port of the SPI Slave receives new data before the previous data has been read, the existing data will be overwritten and lost. If this occurs, the output  $\mathbf{o}$  turns 1 to indicate an overrun error. In the model, as shown in Fig. 2, a counter logic is included at the  $\mathbf{v}$  and  $\mathbf{o}$  ports. This doesn't have much meaning offline.

There are two considerations to note when overrun errors occur:

- The master is not allowed to start transmitting before the slave is up and running. If the slave is booting up while the master is transmitting, then it may receive an incomplete first message, from which it will not be able to recover.

- In order to avoid overruns, the SPI Slave block must be executed faster than the rate at which the SPI Master is sending data.

#### Additional considerations

- Always make sure to provide a common power supply to all the MCUs communicating via SPI.

- From the RT Box LaunchPad Interface User Manual [7], it can be observed that a few SPI signals are connected to digital signals, which would cause interference in SPI communication. Therefore to use SPI, the launchpad board must be disconnected or isolated from the RT Box LaunchPad Interface board.

- Do not use the RT Box to measure the "CLK" signal. This will result in overrun errors.

#### Multi-tasking code

The generated code runs at a base sample time on the MCU or the **Discretization step size**. In this model, the discretization step size of each of the subsystems is set to  $100\,\mu s$ . In order to avoid overruns, the SPI Slave block must be executed faster than the rate at which the SPI Master is sending data. Therefore, multi-tasking code is used to execute the SPI Master block at  $200\,\mu s$ .

Multi-tasking code generation is configured in the **Scheduling** tab of the **Coder + Coder options...** dialog. By changing the **Tasking mode** to multi-tasking and the **Task configuration** to specify, the sample time for each task can be configured. The base sample time is always equal to the **Discretization step size**. The **Sample time** setting for lower priority tasks must be an integer multiple of the base sample time. Up to 15 slower lower priority tasks that execute at different rates can be specified, preserving processor time for the fastest, highest priority task in the application. For further information, refer to the "Code Generation" section in the PLECS User Manual [8].

# 3 Simulation

Each subsystem can be directly converted into target specific code for the corresponding TI LaunchPad hardware.

**Note** Before proceeding, ensure the DIP switch position and jumper configuration on the LaunchPad device are correctly configured. Guidance for each LaunchPad device is provided in the "Tips for Programming C2000 Development Kits" section of the TI C2000 Target Support User Manual [6].

#### Connect the hardware

Next, connect the pin numbers listed below using jumper wires for the desired MCU. To explore the signal exchange via SPI between two different MCU targets, choose any two desired targets. Then configure one of them as a SPI Master and the other one as a SPI Slave.

| 28069 | Master          | Slave           |

|-------|-----------------|-----------------|

| SIMO  | J6-55 (GPIO 24) | J2-15 (GPIO 16) |

| SOMI  | J6-54 (GPIO 25) | J2-14 (GPIO 17) |

| CLK   | J5-47 (GPIO 14) | J1-7 (GPIO 18)  |

| CS    | J6-53 (GPIO 52) | J2-19 (GPIO 19) |

| 280049 | Master          | Slave           |

|--------|-----------------|-----------------|

| SIMO   | J6-55 (GPIO 24) | J2-15 (GPIO 16) |

| SOMI   | J6-54 (GPIO 31) | J2-14 (GPIO 17) |

| CLK    | J5-47 (GPIO 22) | J1-7 (GPIO 56)  |

| CS     | J6-59 (GPIO 27) | J2-19 (GPIO 57) |

| 283775 | Master          | Slave           |

|--------|-----------------|-----------------|

| SIMO   | J6-55 (GPIO 63) | J2-15 (GPIO 58) |

| SOMI   | J6-54 (GPIO 64) | J2-14 (GPIO 59) |

| CLK    | J5-47 (GPIO 65) | J1-7 (GPIO 60)  |

| CS     | J6-53 (GPIO 99) | J1-8 (GPIO 61)  |

| 28379D | Master          | Slave           |

|--------|-----------------|-----------------|

| SIMO   | J6-55 (GPIO 63) | J2-15 (GPIO 58) |

| SOMI   | J6-54 (GPIO 64) | J2-14 (GPIO 59) |

| CLK    | J5-47 (GPIO 65) | J1-7 (GPIO 60)  |

| CS     | J6-53 (GPIO 26) | J2-19 (GPIO 61) |

| 28P650DK9 | Master          | Slave           |

|-----------|-----------------|-----------------|

| SIMO      | J6-55 (GPIO 91) | J2-15 (GPIO 16) |

| SOMI      | J6-54 (GPIO 92) | J2-14 (GPIO 17) |

| CLK       | J8-74 (GPIO 32) | J1-7 (GPIO 18)  |

| CS        | J6-59 (GPIO 94) | J2-19 (GPIO 57) |

#### Flash the MCU

Follow the instructions below to upload the subsystems to a TI MCU.

- Connect the desired MCU to the host computer through a USB cable.

- From the **System** tab of the **Coder + Coder options...** window, select the MCU of interest.

- Next, from the **Target** tab, select the appropriate target from the dropdown menu. Then under the **General** sub-tab, select the desired **Build type**.

- Then, to Build and program the MCU directly from PLECS, choose either Run from Flash or Run from RAM as the **Build configuration**, then select LaunchPad as the **Board** type, and click **Build**.

**Note** If programmed correctly, the LED on the LaunchPad board should blink.

For advanced users who are familiar with Code Composer Studio (CCS), there is an option to Generate code into CCS project. Included with the TI C2000 Target Support package is a folder titled projects. Within the folder there are ZIP archives containing pre-built CCS projects for each MCU. Import the zip archive folder that corresponds to the desired target into CCS. You will notice a new project created in your CCS workspace. Enter the location of the \${workspace\_loc}/dev\_28xx/cg/ folder from the CCS project into the **CCS project directory** field and click **Build**. Then, proceed to build and debug the project as a normal CCS project. Refer to "Quick Start" section of the TI C2000 Target Support User Manual [6] for detailed step-by-step instructions.

#### External Mode

Once the generated code is running on the C2000 target, the user can enter the External Mode to update displays in the PLECS application with real-time values and change certain simulation parameters. The steps below outline how to connect to the target device, with additional debugging details provided in the "Start the External Mode" section of the user manual [6].

- First, from the **System** menu on the left hand side of the **Coder + Coder options...** window, select the desired MCU.

- Then, from the **External Mode** tab, select the **Target device** by clicking / icon next to the **Target** device field.

- Next, click Connect and then Activate autotriggering to observe the results in the subsystem display.

The exchanged SPI signals on a 28379D target are shown in Fig. 2. To learn about the **v** and **o** ports, and tips to handle overrun errors, refer to Section 2.

#### Parameter Inlining

To configure parameters as tunable, open the **Coder + Coder options...** menu and navigate to the **Parameter Inlining** tab. When a component from the schematic is dragged and dropped into the **Exceptions** list, tunable parameters associated with that component will be tunable during runtime. Note

this behavior depends on the **Default behavior** setting, as the **Exceptions** list specifies components which have opposite behavior of the default setting.

In this case, the "TX" inputs to the SPI block can be adjusted on the fly when the model executes on the embedded target device, when connected to External Mode. Changes in the parameters will be reflected in the Scope traces and Display once they take effect.

# 4 Conclusion

This model explores the SPI protocol with the TI C2000 TSP using a simple model.

# References

- [1] TI C2000 Piccolo MCU F280049C LaunchPad Development Kit URL: http://www.ti.com/tool/LAUNCHXL-F280049C.

- [2] TI C2000 Piccolo MCU F28069M LaunchPad Development Kit, URL: http://www.ti.com/tool/LAUNCHXL-F28069M.

- [3] TI C2000 Delfino MCUs F28377S LaunchPad Development Kit URL: https://www.ti.com/lit/pdf/sprui25

- [4] TI C2000 Delfino MCUs F28379D LaunchPad Development Kit, URL: http://www.ti.com/tool/LAUNCHXL-F28379D.

- [5] TI C2000 F28P650DK9 LaunchPad development kit, URL: https://www.ti.com/tool/LAUNCHXL-F28P65X.

- [6] PLECS TI C2000 Target Support User Manual, URL: https://www.plexim.com/sites/default/files/c2000manual.pdf.

- [7] RT Box LaunchPad Interface User Manual, URL: https://plexim.com/sites/default/files/launchpadinterfacemanual.pdf.

- [8] PLECS User Manual,

URL: https://www.plexim.com/sites/default/files/plecsmanual.pdf.

## **Revision History:**

C2000 TSP 1.3.1 First release

Updated the web links C2000 TSP 1.4.5

Updated SPI mode settings C2000 TSP 1.5.2

#### **How to Contact Plexim:**

+41 44 533 51 00 Phone Fax +41 44 533 51 01

Plexim GmbH Mail

Technoparkstrasse 1

8005 Zurich Switzerland

info@plexim.com Email

Web http://www.plexim.com

#### Embedded Code Generation Demo Model

## © 2002-2023 by Plexim GmbH

The software PLECS described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from Plexim GmbH.

PLECS is a registered trademark of Plexim GmbH. MATLAB, Simulink and Simulink Coder are registered trademarks of The MathWorks, Inc. Other product or brand names are trademarks or registered trademarks of their respective holders.