RT Box DEMO MODEL

### Single-Phase Inverter

Last updated in RT Box Target Support Package 2.1.7

# 1 Overview

This demo model features a single-phase grid-connected inverter operating at  $50 \,\mathrm{kW}$  and unity power factor. This document describes the implementation of the power stage and controls using the PLECS electrical and control domains.

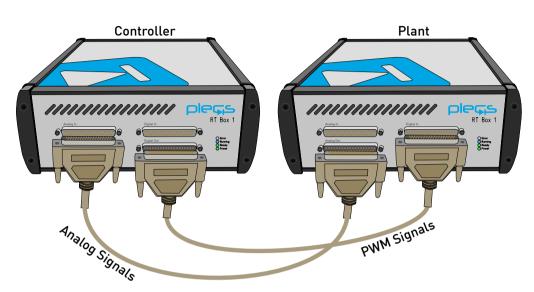

The plant and the controller models are split into two distinct subsystems. The subsystem representing the plant is deployed on one RT Box and the subsystem representing the controller is deployed on a second RT Box. The two RT Boxes are connected front-to-front in a virtual prototyping configuration with two 37 pin Sub-D cables to exchange digital PWM signals and analog current measurements. Virtual prototyping is a potential first step when developing real-time models for Hardware-in-the-loop (HIL) or rapid control prototyping (RCP) applications.

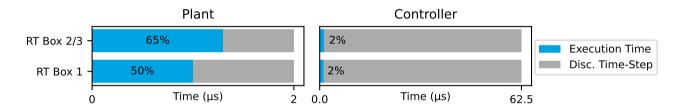

The chosen discretization step sizes and average execution times for each subsystem in the singlephase inverter model are shown in Fig. 1. Real-time execution on the RT Box requires the model to execute using a fixed-step solver. The discretization step size parameter specifies the base sample time of the generated code and is used to discretize the physical model and control domain state-space equations. The execution time represents the actual time it takes to execute one discrete step of the PLECS model on the RT Box hardware. The processor loading is the ratio of the execution time to the discretization step size.

Figure 1: Performance overview for the execution on two RT Boxes

#### 1.1 Requirements

To run this demo model, the following items are needed (available at www.plexim.com):

- Two PLECS RT Boxes and one PLECS and PLECS Coder license

- The RT Box Target Support Package

- Follow the step-by-step instructions on configuring PLECS and the RT Box in the Quick Start guide of the RT Box User Manual.

- Two 37 pin Sub-D cables to connect the boxes front-to-front.

Note that this demo model is targeted at two RT Boxes application, with one running the Plant and the other running the Controller. In this way, the execution time of each real-time target is minimized. Besides, the setup can easily transition to a HIL or RCP test later on.

However if the user has only one RT Box available, please check the corresponding models targeted for one RT Box application. In this case, two 37 pin Sub-D cables are still needed to connect in front Analog Out interface with Analog In interface, and Digital Out interface with Digital In interface.

- For RT Box 2 and 3, by default the multi-tasking feature is enabled in this demo. "Controller" part is circled with a Task frame block, and runs in one core. The rest of the circuit on the schematic belongs to the "Base task", and runs in another core. In this way the computational effort is split onto different cores. Please check the default setting under **Scheduling** tab of the **Coder options...** window.

- For RT Box 1, single-tasking should be used which runs both the Plant and the Controller on the same one core of the RT Box 1.

**Note** This model contains model initialization commands that are accessible from:

PLECS Standalone: The menu Simulation + Simulation Parameters... + Initializations

*PLECS Blockset:* Right click in the **Simulink model window + Model Properties + Callbacks + InitFcn**\*

### 2 Model

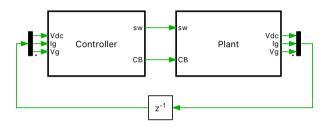

The top level schematic contains two separate subsystems representing the plant ("Plant") and controller ("Controller") models, as shown in Fig. 2. Both subsystems are enabled for code generation from the **Edit + Subsystem + Execution settings...** menu. This step is necessary to generate the model code for the RT Box. Additional delays in the feedback path are also modeled.

Figure 2: Top level schematic of the controller and plant model

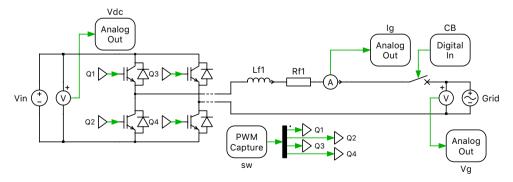

#### 2.1 Power Circuit

The power circuit is supplied by a DC voltage source with  $V_{dc} = 750$  V. The H-bridge is composed of two IGBT Half Bridge power module components. The switching signals  $Q_1, Q_2, Q_3$  and  $Q_4$  are captured by the PWM Capture block from the PLECS RT Box Target Support library. The modeling of the power module components and the sub-cycle averaged handling are described in the work of [2]. The output of the H-bridge is connected to the power grid via a filter inductor and a circuit breaker. The low voltage power grid is modeled by an ideal AC voltage source with  $V_{\rm rms} = 220$  V and f = 50 Hz. The measurements of DC voltage, grid voltage and grid current are routed out of the subsystem via Analog Out components from the PLECS RT Box Target Support library. The scaling factors and offsets are configured to limit the analog output voltages within the range [-4 V, +4 V].

Figure 3: Power circuit of the single phase grid-connected inverter

#### 2.2 Controls

The closed-loop controller regulates the line current to be in phase with the grid voltage.

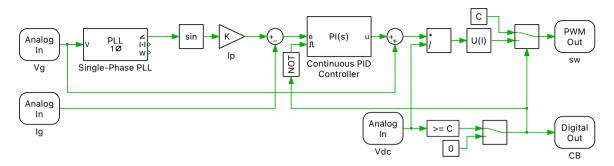

Figure 4: Controller model of the single-phase grid-connected inverter

A phase-locked loop (PLL) based on the quadrature signal generator is included to detect the electrical angle and frequency of the power grid. More details about this PLL structure have been introduced in [1].

The phase angle output of the PLL is converted into the reference signal of the grid current via one Trigonometric Function block and a proportional gain  $I_p$ .  $I_p$  indicates the amplitude of the desired grid current. The internal structure of the subsystem "Controller" is realized by a proportional-integral (PI) regulator. The parameters  $K_p$  and  $K_i$  of the PI regulator are set using the Optimum Magnitude rule. More details about the parameter calculation are included in the description of the "Boost Converter" demo model of the RT Box Target Support Package. Moreover, the anti-windup logic is included, and the gain  $K_{\rm bc}$  is determined by  $K_{\rm bc} = K_i/K_p$ .

At the output of the regulator, a feedforward of the grid voltage is added to improve the transient response. After that, the signal is divided by the DC voltage and fed to the PWM Out block as a modulation index. The PWM Out block has been configured to be synchronized with the execution step size of the controller, if this model is programmed into the real-time target.

# **3** Simulation

This model can run both, in offline mode on a computer or in real-time mode on the PLECS RT Box. For the real-time operation, two RT Boxes (referred to as "Plant" and "Controller") need to be set up as demonstrated in Fig. 5. Please follow the instructions below to run a real-time model on two RT Boxes:

- Connect the Analog Out interface of the "Plant" RT Box to the Analog In interface of the "Controller" RT Box, and the Digital In interface of the "Plant" RT Box to the Digital Out interface of the "Controller" RT Box (e.g. using two DB37 cables shown in Fig. 5).

- From the **System** tab of the **Coder options...** window, select the "Plant" and **Build** it onto the "Plant" RT Box. Then, select "Controller" and **Build** it onto the "Controller" RT Box.

- Once the models are uploaded, from the **External Mode** tab of the **Coder options...** window, **Connect** to both RT Boxes and **Activate autotriggering**.

**Note** As shown above, during runtime the Manual Signal Switch before the Digital Out named "CB" in the "Controller" subsystem in its default Up position enables switching. Change it to the Down position disables switching and also resets the PI Controller integral part.

Figure 5: Hardware configuration for the real-time operation of the demo model

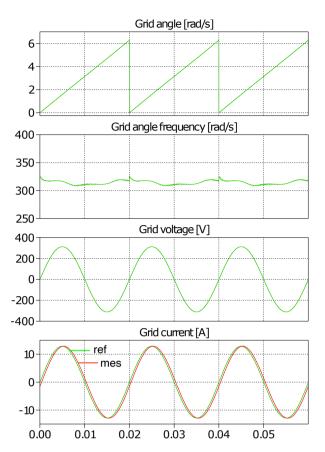

During the real-time operation under **External Mode** the measurements and intermediate signals on the controller box can be observed using in the PLECS Scope "Elec". The grid phase angle, angular frequency detected by the PLL, and measured grid voltage and current are shown in Fig. 6. In the plot at the bottom, the reference current and the measured current are compared with each other. The reference amplitude of the grid current can be changed by varying the gain block "Ip" in the "Controller" subsystem.

# 4 Conclusion

This model demonstrates a single-phase grid-connected inverter model which can run in both offline simulation and real-time operation for Hardware-in-the-loop testing and rapid control prototyping.

### References

- [1] R. Teodorescu, M. Liserre and P. Rodriguez, "Grid converters for photovoltaic and wind power systems", IEEE, Wiley, 2011

- [2] J. Allmeling and N. Felderer, "Sub-cycle average models with integrated diodes for real-time simulation of power converters," 2017, 10.1109/SPEC.2017.8333566

Figure 6: Real time measurements and intermediate signals obtained with PI regulator on the RT Box "Controller"

#### **Revision History:**

RT Box Target Support Package 1.8.3 RT Box Target Support Package 2.1.5

RT Box Target Support Package 2.1.7

First release Turn on Assertions in the IGBT Full Bridge and add deadtime in the PWM Out block Use Single-Phase PLL and PI Controller components from the library

#### How to Contact Plexim:

| 1 | $+41 \ 44 \ 533 \ 51 \ 00$                                       | Phone        |

|---|------------------------------------------------------------------|--------------|

|   | $+41 \ 44 \ 533 \ 51 \ 01$                                       | Fax          |

|   | Plexim GmbH<br>Technoparkstrasse 1<br>8005 Zurich<br>Switzerland | Mail         |

| @ | info@plexim.com<br>http://www.plexim.com                         | Email<br>Web |

#### RT Box Demo Model

© 2002–2022 by Plexim GmbH

The software PLECS described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from Plexim GmbH.

PLECS is a registered trademark of Plexim GmbH. MATLAB, Simulink and Simulink Coder are registered trademarks of The MathWorks, Inc. Other product or brand names are trademarks or registered trademarks of their respective holders.