RT Box DEMO MODEL

## SPI interface demo on a single RT Box

Last updated in RT Box Target Support Package 2.2.1

# 1 Overview

The Serial Peripheral Interface (SPI) is a synchronous serial communication interface specification used for short-distance communication, primarily with peripheral devices. SPI devices communicate in full duplex mode using a master-slave architecture between a single master and multiple slaves.

The SPI Master and SPI Slave block from the RT Box Target Support Package implement SPI communication via digital outputs/inputs. There are 2 SPI modules available on the RT Box. Each SPI module can output data on up to 4 paralleled data channels (using a common clock and chip select signal).

This demo model shows:

- a demo scenario that wires the SPI Master digital output channel with the SPI Slave digital input channel (i.e. SIMO for Slave-In-Master-Out), as well as the SPI Slave digital output channel with the SPI Master digital input channel (i.e. SOMI for Slave-Out-Master-In),

- how to configure the parameters inside the SPI Master and the SPI Slave block,

- SPI transmission within a single or multiple RT Box model steps.

One additional model shows the use case of the RT Box as SPI master connected to an external ADC device as the SPI slave. This additional model is explained in Appendix, and can be accessed by opening the demo model folder.

## 1.1 Requirements

- One PLECS RT Box and one PLECS Coder license.

- The RT Box Target Support Package (minimum version 2.2.1).

- Follow the step-by-step instructions on configuring PLECS and the RT Box in the Quick Start guide of the RT Box User Manual.

- Wire the Digital Output channel 0, 1, 2, 3, 4 respectively to the Digital Input channel 0, 1, 2, 3, 4 on the front pannel of the RT Box.

# 2 Model

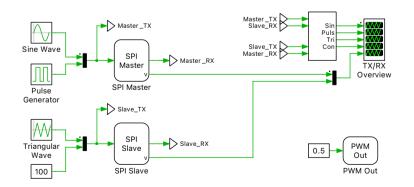

This demo model uses the SPI1 module as the SPI Master and the other SPI2 module as the SPI Slave on the same RT Box.

### Figure 1: Subsystem circuit schematic for the SPI Master-Slave demo

The circuit schematic is shown in Fig. 1. A Sine wave and a Pulse wave are packed into two 16-bit words and transmitted out from the SPI Master data output channel. With the hardware wiring, it is received at the SPI Slave data input channel. Likewise, a Trianglular wave and a Constant value are transmitted out from the SPI Slave data output channel to the SPI Master data input channel. Both

the transmitted original signals and the received signals are displayed in the Scope in Fig. 1 for comparison.

Additionally, a PWM Out block generates a PWM signal with 0.5 duty cycle synchronized with the RT Box model step size by configuring its **Synchronization with model step** option as Enabled. This PWM signal can be used as a reference to observe the different behaviors of SPI transmission within a single or multiple RT Box model steps.

Fig. 2 shows the mask content of the SPI Master block. For the fields not mentioned in the following explanation, please refer to the **Help** page of the SPI Master block.

## SPI Master Setup tab

| Implement SPI communication via data channels. | digital outputs/inputs.One slave can have up to four | parallel  |

|------------------------------------------------|------------------------------------------------------|-----------|

|                                                |                                                      |           |

|                                                | Setup Input Output                                   |           |

| SPI module:                                    | Bits per word:                                       |           |

| SPI1                                           | <ul> <li>16</li> </ul>                               | <b>()</b> |

| SPI clock frequency [Hz]:                      | Bit order:                                           |           |

| 2e6                                            | MSB first                                            | 0         |

| Delay first clock pulse after CS ac            | ive [ticks]: Skew-matched clock input:               |           |

| 1                                              | Enabled                                              | <b>O</b>  |

| Hold CS active after last clock pul            | e [ticks]: Number of parallel data channels:         |           |

| 1                                              |                                                      | <b>O</b>  |

| Delay CS after simulation step:                | Words per transmission (up to 127):                  |           |

| Minimum                                        | $\bigcirc \qquad 2$                                  |           |

| CS delay time [s]:                             | Sample time:                                         |           |

| 0.5e-6                                         | Ts_spi                                               |           |

| Mode [CPOL,CPHA]:                              |                                                      |           |

| 0 - [0,0]                                      | 0                                                    |           |

|                                                |                                                      |           |

### Figure 2: Mask content of the SPI Master block

- SPI module: there are 2 SPI modules integrated into the RT Box for choosing, either SPI1 or SPI2.

- The **Delay first clock after CS active** and **Hold CS active after last clock pulse** fields are used in case of special timing needed between the clock signal and CS (chip select) signal. In this demo the default value of 1 (tick) is used in each field.

- The **Delay CS after simulation step** is useful to adjust the beginning of SPI data transmission with regards to the RT Box simulation step. In this demo, Minimum is used by default.

- Mode [CPOL, CPHA]: Note that the same SPI mode has to be configured between the SPI Master and an external SPI Slave device to ensure correct data interpretation.

- Skew-matched clock input can be enabled when the signal transmission delay from the master output to its input exceeds half an SPI clock period. When enabled, the corresponding **Digital input channel for skew-matched SPI clock** under **Input** tab has to be specified to receive the incoming clock, otherwise this field is greyed out.

- Number of parallel data channels: Note that the dimension of the Digital input channel(s) for SPI data and Digital output channel(s) for SPI data under Input and Output tabs has to match the number chosen here. In this demo only 1 data channel is used.

- Words per transmission: In this demo, one word is used for the Sine wave and the other word is used for the Pulse wave.

- **Sample time**: Putting 0 here means that the SPI transmission happens within every single model step. The SPI transmission can also be extended over multiple model steps by putting a number here which is an integer multiple of the model step size. In the following section, it showcases both scenarios. Besides, putting -1 means to inherit the sample time of the Atomic Subsystem or Task frame that this SPI Master block resides in.

## SPI Master Input and Output Tabs

Since each SPI module can only output one SPI clock signal and one CS signal, the **Digital output** channel for SPI clock and **Digital output channel for CS** require both a single channel number.

## **SPI Slave**

The mask content of the SPI Slave block is the same as that of the SPI Master, except for several CS (Chip Selection) timing related fields. Thus it is not discussed again.

# **3** Simulation

From the **System** tab of the **Coder options...** window, select the "Subsystem" and go to the **Target** tab. **Build** the "RT Box" model onto the RT Box. Once the model is uploaded, from the **External Mode** tab of the **Coder options...** window, **Connect** to the RT Box and **Activate autotriggering**. The real-time simulation results can be observed via PLECS Scope called "TX/RX Overview". One can also change the Constant with value of 100 into, for example 200, and observe the immediate change in the received value.

## 3.1 SPI Transmission within a Single Model Step

This is the default setup in the Model initialization commands of this demo model. It is done by enabling type = 'single', which sets:

- RT Box discretization step size =  $20 \,\mu s$

- SPI transmission sample time =  $20 \,\mu s$

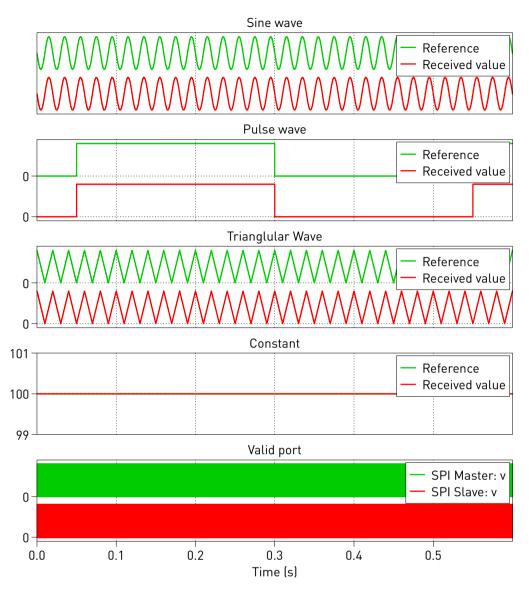

Once the real-time simulation is running on the RT Box and the external mode is enabled, the most important waveforms on "TX/RX Overview" Scope are shown in Fig. 3. The received values match their transmitted original values in terms of signal amplitude and frequency. This validates the SPI Master-Slave functionality on the RT Box.

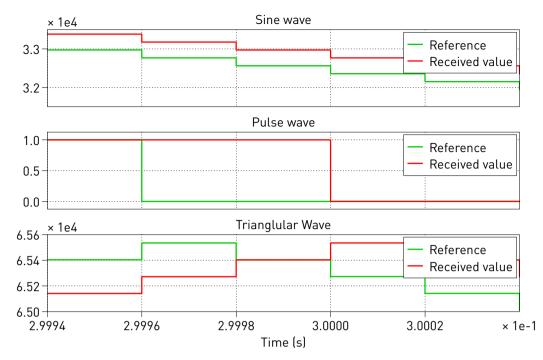

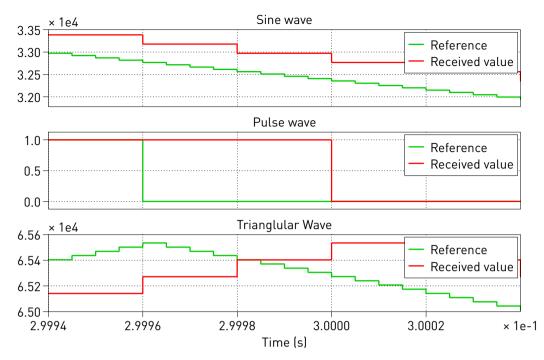

Fig. 4 shows the zoom-in of Fig. 3 around 0.3 s. The incoming SPI Master data exhibits a staircase waveform with step size of  $20 \,\mu s$ , which equals to the RT Box discretization step size. There is a delay of two SPI transmission intervals between the outgoing reference signal and the received data.

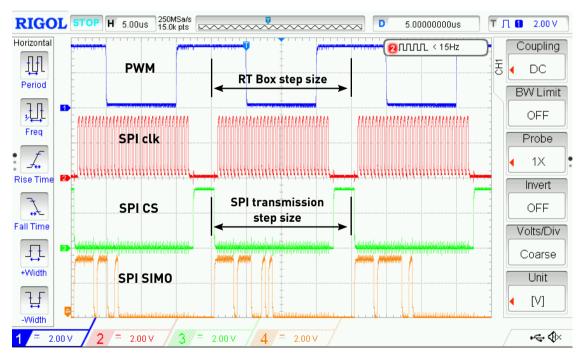

For more insight on the timing, an external oscilloscope is used to measure the different digital channels and the RT Box step size. In Fig. 5 probe CH1 shows the 0.5 duty cycle PWM synchronized to the  $20 \,\mu$ s model step size. Since the PWM is generated with positive polarity, from the center of the high

Figure 3: Real-time simulation result on PLECS Scope for SPI transmission within a single model step

state to the center of the next high state marks exactly one model step. One can see that in this scenario, the SPI transmission happens within every RT Box model step. Note that due to limited number of channels on the oscillosocpe, only the Slave-In-Master-Out (SIMO) data bus is probed in Fig. 5 and Slave-Out-Master-In (SOMI) data is not measured.

## 3.2 SPI Transmission over Multiple Model Steps

This scenario can be chosen by commenting out the previous type = 'single' and enabling type = 'multi' in the model initialization commands of this demo model. This sets:

- RT Box discretization step size =  $5 \,\mu s$

- SPI transmission sample time =  $20 \,\mu s$

This is to demonstrate the case when the SPI transmission time (approx. SPI clock period x Bits per word x Words per transmission) requires more time than what a single RT Box step offers. Note that the SPI transmission interval can only be integer multiples of the RT Box step size.

Figure 4: Zoom-in around 0.3 s of the real-time simulation result on PLECS Scope for SPI transmission within a single model step

Figure 5: External oscilloscope measurement for SPI transmission within a single model step

The real-time simulation waveforms on the "TX/RX Overview" Scope look similar to Fig. 3 on a large time scale. However, the zoom-in shown in Fig. 6 reveals the difference. For example, the Sine wave reference signal is discretized with 5  $\mu$ s now, while the incoming SPI data is still updated every 20  $\mu$ s. The complete SPI transmission takes 4 full RT Box calculation steps. There are still two SPI transmission steps delay in the loop-back scenario between the reference signal and the received data.

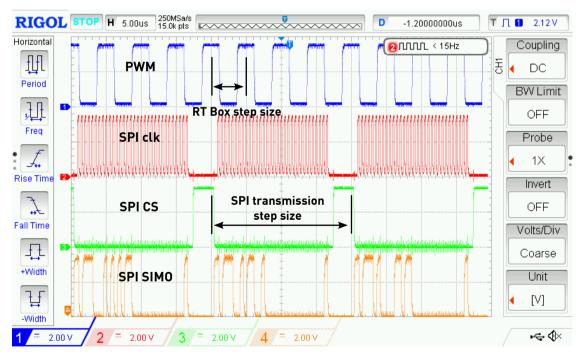

Fig. 7 provides more insight with the oscilloscope measurement. Probe CH1 shows the 0.5 duty cycle

Figure 6: Zoom-in around 0.3 s of the real-time simulation result on PLECS Scope for SPI transmission over multiple model steps

Figure 7: External oscilloscope measurement for SPI transmission over multiple model steps

PWM indicating the new 5  $\mu s$  model step size. CH2 to CH4 show the SPI transmission at 20  $\mu s$  sample time, which are exactly 4 times a model step.

## 4 Conclusion

This RT Box demo model demonstrates a Master-Slave test using the integrated SPI interface on the RT Box. It shows how to set up the SPI Master and Slave blocks in a PLECS model. The demo model runs in both offline and in real-time simulation.

# 5 Appendix

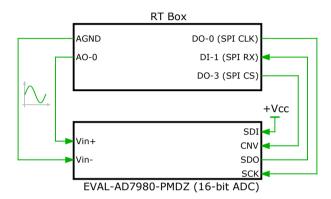

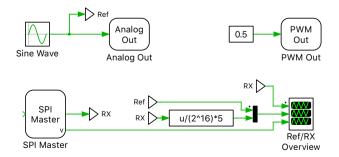

For the SPI transmission with in a single model step size case, a more advanced demo is provided with the name spi\_demo\_adc under the demo model folder. Fig. 8 depicts the setup and pin connection for this scenario.

### Figure 8: Pin connection between the RT Box and the external ADC board for the advanced SPI demo

The RT Box works as the SPI Master and generates a sinusoidal analog signal between 0.5 V and 4.5 V at 50 Hz. The 16-bit ADC evaluation board (EVAL-AD7980-PMDZ) converts this analog signal into digital values and works as the SPI Slave to send the converted data to the RT Box SPI interface.

Note that in this demo the RT Box SPI CS signal is used as the CNV (conversion start) signal of the ADC and the ADC SDI pin is tied up to the supply voltage. Please see section "3-WIRE CS MODE WITHOUT BUSY INDICATOR" in [1]. In case of using two AD7980 devices together, one might need specific timing patterns of CNV, and CS1 CS2 for SDI pin of each ADC. In this case, duty cycle and carrier phase shift of the PWMs synchronized with the SPI transmission sample time can be properly adjusted to achieve the desired signals.

The RT Box subsystem circuit schematic is shown in Fig. 9. Scope "Ref/RX Overview" shows the comparison between the analog reference signal sent out from the RT Box and received SPI data after external ADC conversion.

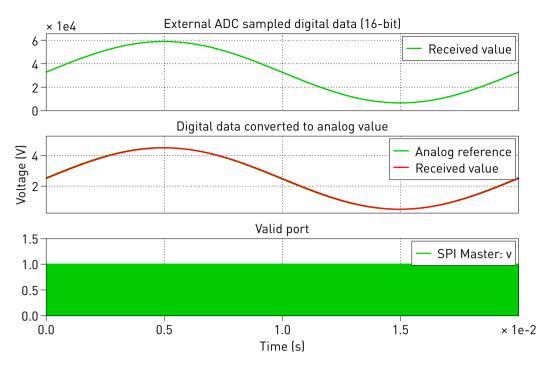

Once the model is uploaded onto the RT Box and the external mode is enabled, the real-time simulation results can be observed as shown in Fig. 10.

Figure 10: Real-time simulation result on PLECS Scope of the advanced SPI demo

## References

[1] Analog Devices AD7980 datasheet [Online]. Available: https://www.analog.com/media/en/technicaldocumentation/data-sheets/AD7980.pdf.

### **Revision History:**

RT Box Target Support Package 2.1.1 RT Box Target Support Package 2.2.1 First release Include SPI Slave

### How to Contact Plexim:

| $+41 \ 44 \ 533 \ 51 \ 00$                                       | Phone                                                                                                   |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| $+41 \ 44 \ 533 \ 51 \ 01$                                       | Fax                                                                                                     |

| Plexim GmbH<br>Technoparkstrasse 1<br>8005 Zurich<br>Switzerland | Mail                                                                                                    |

| info@plexim.com                                                  | Email                                                                                                   |

| http://www.plexim.com                                            | Web                                                                                                     |

|                                                                  | +41 44 533 51 01<br>Plexim GmbH<br>Technoparkstrasse 1<br>8005 Zurich<br>Switzerland<br>info@plexim.com |

#### RT Box Demo Model

© 2002–2022 by Plexim GmbH

The software PLECS described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from Plexim GmbH.

PLECS is a registered trademark of Plexim GmbH. MATLAB, Simulink and Simulink Coder are registered trademarks of The MathWorks, Inc. Other product or brand names are trademarks or registered trademarks of their respective holders.