THE SIMULATION SOFTWARE PREFERRED BY POWER ELECTRONICS ENGINEERS

# **Technical Specifications**

▶ Processor CPU clock speed 1 GHz

► Analog input Channels Resolution Voltage range Input type Sample rate Input impedance Protection

16 16 bit -10 ... 10 V Differential 2 Msps 1 MΩ, 24 pF Overvolt., ESD D-SUB 37 pin

► Analog output Channels Resolution Voltage ranges

-10 ... 10 V 0 ... 10 V -5 ... 5 V 0 ... 5 V 2 Msps 0 MΩ

Sample rate Output impedance Output current Protection

≤ 5 mA Short-circuit, Overvolt., ESD D-SUB 37 pin

▶ Digital input Channels

3.3 V (5 V tolerant)

Protection

Overvolt., ESD D-SUB 37 pin

▶ Digital output Channels Logic levels Output

5 V, 3.3 V 250 Ω

impedance Protection

Short-circuit, Overvolt., ESD D-SUB 37 pin female

**►** Connectivity Ethernet

High speed **USB** device RJ-45, Gigabit 4 x SFP+, 6.25 Gbps per lane USB 2.0 high speed, Type A USB 2.0,

Host PC

Type B SD card Firmware

► Power supply

50 ... 60 Hz

**►**I Size  $D \times W \times H$

# **PLECS RT BOX®**

Hardware-in-the-Loop (HIL) Platform

Plexim's product line now includes real-time simulation hardware to provide a complete, one-stop solution for modern power electronic system development teams.

The PLECS RT Box is a state-of-the-art real-time simulator designed for HIL testing of complex power converter systems. The unit may also be scaled up for more demanding HIL applications, such as modular multi-level HVDC converters.

THE SIMULATION SOFTWARE PREFERRED BY POWER ELECTRONICS ENGINEERS

#### Trial license

Get a free trial license valid for 30 days!

▶ plexim.com/trial

#### **Seminars**

Participate and learn all aspects of the PLECS simulation software.

▶ plexim.com/events/ seminars

### **Training**

Become an expert with training at your company. Contact us

► info@plexim.com

# Services and support

Benefit from the expertise of our engineers.

▶ plexim.com/support

#### Store

Find our current price list at

▶ plexim.com/store

#### **Conferences**

Meet us at conferences worldwide.

▶ plexim.com/events

### Contact

For inquiries please contact us.

- ▶ plexim.com/company/ contact

- ▶ info@plexim.com

# **Agile System Design Using PLECS**

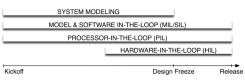

System modeling is crucial to power electronics product development. It facilitates early design decisions and formulation of system and subsystem requirements. An agile development process based on multiple short design iterations provides opportunities to learn lessons and adjust these requirements.

A system model maintained throughout the development process also serves as a virtual test bed for subsystem iterations. Developing systems using the PLECS toolchain can keep the different subsystems in sync during their respective design iterations.

Using PLECS tools with an agile design flow

"In-the Loop" testing of control software (SIL/PIL) can be applied very early in development, minimizing risk of subsystem incompatibility. As control hardware becomes available, HIL testing can be used to increase test coverage.

The PLECS RT Box, together with the PLECS circuit simulator and PLECS Coder, provides a complete and consistent solution for system-level verification and validation of control software and hardware subsystems.

# **Code Generation**

The PLECS Coder can generate C code from a PLECS model for execution on real-time hardware. This requires the model to be discretized to run at a fixed sample frequency. Due to the fast time constants inherent in power conversion systems, the step size typically is on the order of µs. The ideal step size is a compromise between system model fidelity and accuracy of the simulation results.

To assist the developer with this tradeoff, the PLECS Coder supports simulating generated discretized code within PLECS before it is deployed onto the real-time hardware.

This allows inspecting signal waveforms for different use cases and ensuring they are accurate enough for system testing purposes.

# **Specialized Switch Models**

Specifically for real-time code generation, PLECS' component library includes Power Modules. These blocks implement power-stage topologies such as choppers, 2 and 3-level half bridges, and cascaded half and full bridges, all optimized for real-time simulation of models containing many switches.

# Simulation Speed

The most meaningful metric when comparing the "speed" of real-time simulators is overall roundtrip latency, i.e. total time elapsed from measuring inputs to updating outputs. Delays depend on the underlying hardware topology. Several approaches exist, all with tradeoffs.

|             | DSP | FPGA | SOC |

|-------------|-----|------|-----|

| Performance | ++  | ++   | +   |

| Flexibility | ++  | -    | ++  |

| Latency     |     | ++   | +   |

HIL hardware implementation options

The PLECS RT Box is based on an SOC, optimizing I/O latency, numerical performance and modeling flexibility. The latest generation of 16-bit ADC and DAC chips ensures excellent signal resolution. The digital capture module can resolve PWM signals at 10 ns.

# Outlook

The PLECS RT Box is designed with the future in mind. With its high-speed communication interface, multiple RT Boxes can operate in parallel or in a master/slave arrangement. Such configurations leverage PLECS solver and coder technologies currently being developed, making the platform even more powerful and suitable for complex, large scale real-time simulations.

Plexim's product portfolio now covers all aspects of virtual system testing. We offer a one-stop solution with a unified user experience and the trusted power of PLECS.