PLECSのデモモデルに含まれている、この事例では、定格出力:700V/12.25KWの電源回路(VIENNA整流回路)をモデリングしています。 制御ロジックとしては、複数のフィードバック・ループにより電源回路を制御するシステム(カスケード制御)が採用されています。

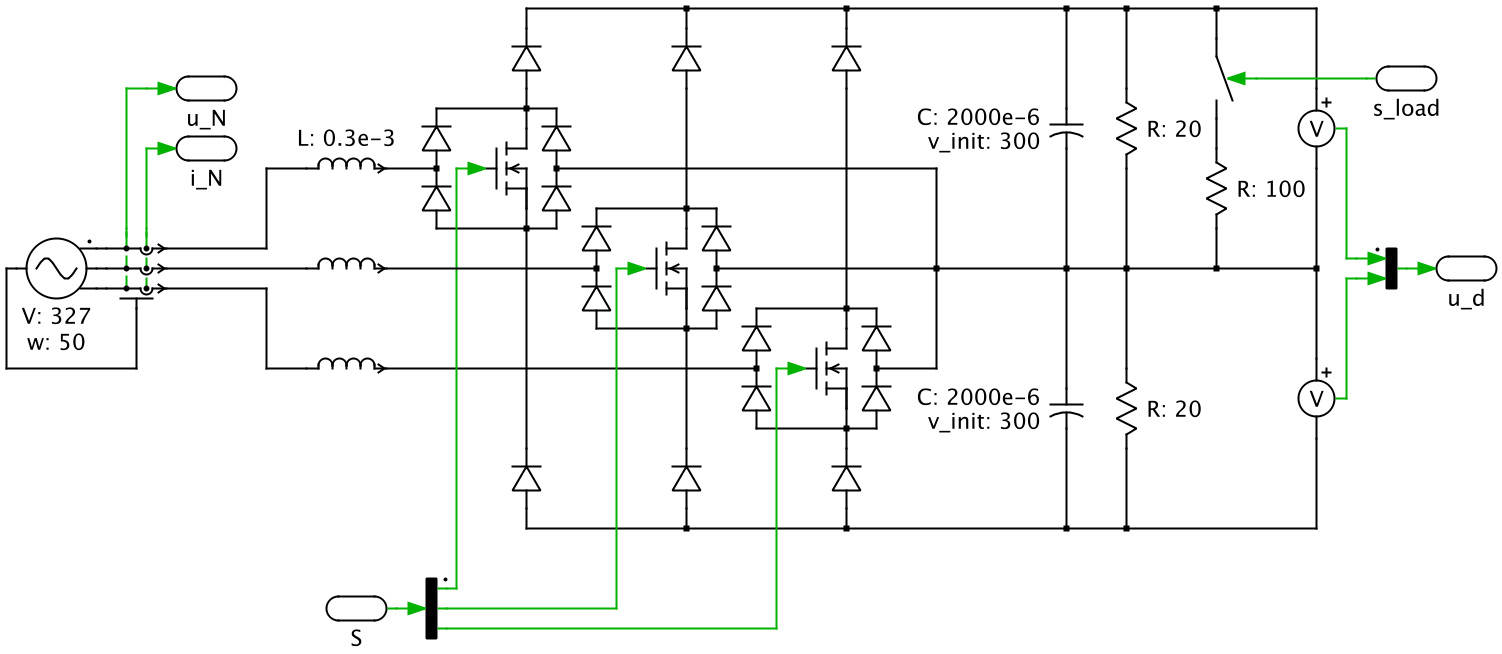

電源回路

VIENNA整流回路は、3相3レベルのPWM AC/DCインバータです:

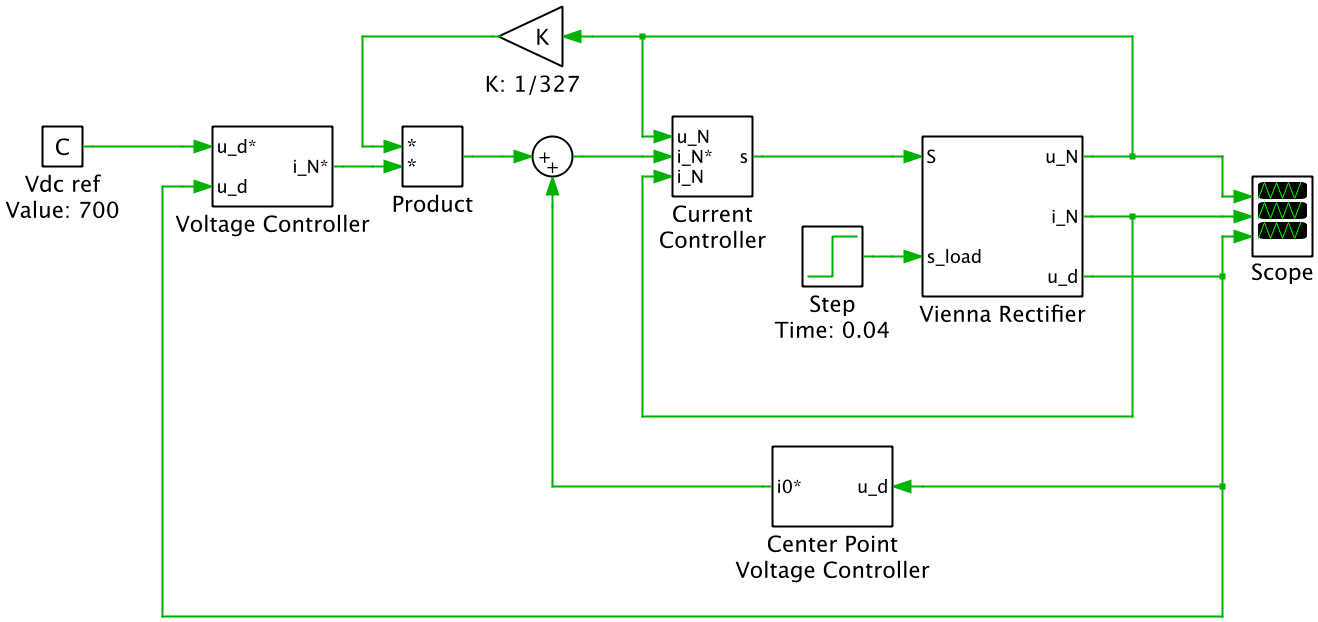

制御ロジック

制御器はサブシステムブロック内に実装されています。 制御器は、電流ループ、直流中性点電圧ループ、直流電圧ループのカスケード接続によって構成されています。

直流電圧ループは、PI制御器を使用して、2つのキャパシタから出力される電圧を加算して制御します。 制御器からの出力は、電源電流の振幅IN*の参照信号となります。 この振幅は、3相電源電流の振幅IN*を検出するため、電源電圧と同期した、3相正弦波信号に乗算されます。 この正弦波信号は、簡略化のため、検出された電源電圧により、直接生成されます。

電源電流の参照信号は、直流電流参照信号i0*によってオフセットされます。 この直流参照信号は、2つのキャパシタから出力される電圧差を制御するPI制御器の出力信号です。

最終的に、電源源流参照信号は、パワー半導体を駆動するゲート信号を生成するヒステリシス電流制御器で使用されます。 VIENNA整流回路の動作原理により、電源の各相電圧が負の間、これに対応するトランジスタのゲート信号は、反転されます。

シミュレーション

シミュレーションでは、急激な非対称負荷に対する出力電圧の制御応答が確認できます。 スコープには、電源電圧正弦波、ヒステリシス制御された電源電流、2つのキャパシタから出力される直流電圧波形が表示されます。

シミュレーションを開始すると、2つのキャパシタは、300V(初期条件)から350Vに、急速充電されます。 シミュレーション開始後0.04秒に、負荷が非対称になります。 中性点電圧制御器がない場合は、キャパシタ電圧が不均衡になりますが、 制御器が作動する場合は、その差は僅かとなり、約0.1秒後に再度、均衡状態になります。