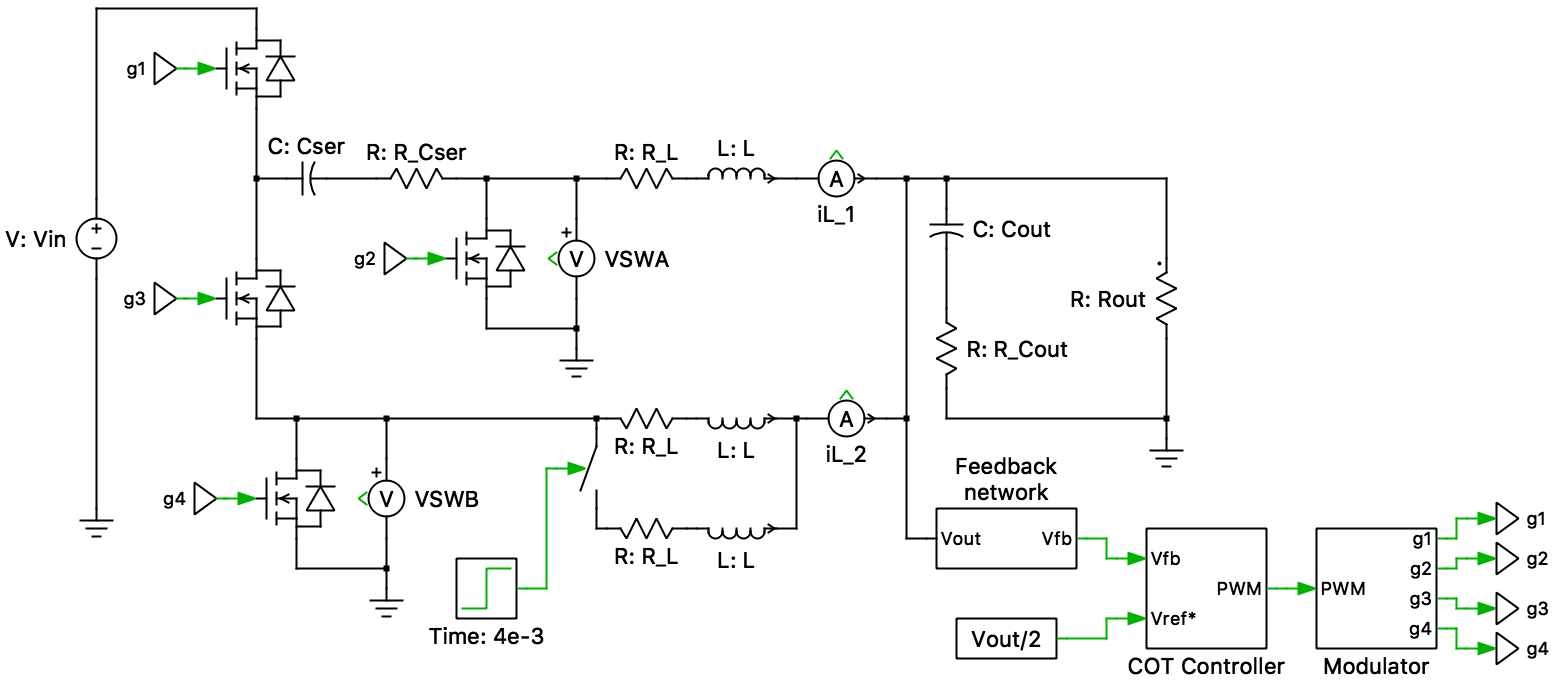

PLECSのデモモデルに含まれている、この事例では、TI社から提出された技術白書「Design of a high-frequency series capacitor buck converter」に記述されている、 COT(Constant On-Time)制御2相直列キャパシタ降圧コンバータ回路を解析しています。

電源回路

直列キャパシタ降圧コンバータ回路は、スイッチトキャパシタ回路と、 2相降圧コンバータ回路を組み合わせた、DC/DC変換用回路トポロジーです。 直列キャパシタ回路は定格入力電圧の半分となる、2:1の電圧降下を実施するため、出力フィルタの視点で考えると、 入力電圧の半分を降圧するコンバータ回路と言えます。 スイッチノード(VSWAおよびVSWB)は、降圧コンバータに対する全入力電圧ではなく、 半分の入力電圧値を整流するため、スイッチング損失は低減化されます。

コンバータには50%のデューティ比制限が設定されており、直列キャパシタ回路によって生成される2:1の電圧降下と組み合わせ、 負荷側の最大電圧出力は、入力電圧の1/4になります。実用的な電圧出力の制限値は、入力電圧の1/5程度である場合が多いですが、 この例題では、制限値を入力電圧の1/10としています。

制御ロジック

回路の出力電圧を制御するため、 COT(Constant On-Time)制御が採用されています。 これは、スイッチのターンオン時間を、一定に指定する可変周波数制御方式です。 制御器はPWMランプ信号として、リップル電圧出力(Vfb)を参照します。 この信号は電圧指令値(Vref*)と比較するため、リップル電圧が必要になります。 これは出力キャパシタESRによって提供されます。比較器はフィードバック電圧(Vfb)を参照して、 フィードバック出力が指令値より低い場合、ハイサイドスイッチのターンオン時間をトリガします。 ターンオン時間は一定のため、制御器はターンオフ時間のみを変調します。 「Min Off-time」ブロックは、急激な負荷変動時のインダクタ飽和を防止します。 COT制御は、特に大電圧の降圧(低デューティ比)に対して有効です。

PLECSステートマシンブロックを使用してCOT制御を実装する例題は、 PLECSデモモデルの「ステートマシンによるCOT制御降圧コンバータ」を参照して下さい。

シミュレーション

例題のモデルは、入力電圧12 Vに対して定常動作する、 POL(Point of Load)電圧レギュレータの適用事例になっています。 直列キャパシタ回路の平均出力電圧は、入力電圧の約半分(6V)で、 スイッチノード出力電圧VSWA/VSWBも、入力電圧の半分(6V)に制限されています。 降圧コンバータ回路の負荷側出力電圧は、入力電圧の約1/10(1.2V)になります。 コンバータのインダクタ電流は完全に平衡しており、どれか1つのインダクタパラメータ値を変化させることによって、これを確認可能です。

Try it

モデルは、PLECS Blockset/Standaloneの「PLECSデモモデル」ライブラリに格納されています。